- HomePage

- Course calendar

- Contact Info

- Computing

- Project

- Exams

- Miscellaneous

- Learn@UW

- AllRecentChanges

- All Pages

Tasks

Homework 2 Testbench Example

If you've written your verilog but are unsure of how to proceed with using the test benches that we've supplied here is a brief example of what your debug process might look like. This example uses the shifter testbench for problem 1.

Running the Testbench

You can run the testbench from the command line using the supplied wsrun.pl script. The script will require at least two arguments, the first is the name of the top level module that you would like to simulate (not the file name), and the remaining required arguments are all of the verilog files containing the module and all submodules that the top level uses. So for example for question 2 it would be run as such assuming you did not use any submodules in your shifter:

wsrun.pl shifter_hier_bench clkrst.v shifter_hier_bench.v shifter_hier.v shifter.v

Alternatively it can be run as:

wsrun.pl shifter_hier_bench *.v

But note that all '.v' files in your current directory will attempt to be compiled and even if a file that is unused does not compile the simulation will not be able to run.

If your testbench has run correctly you should see some output that looks like the following:

-------------------------------------------------

Step: 1

Compiling the following verilog files: clkrst.v shifter_hier_bench.v shifter_hier.v shifter.v

Top module: shifter_hier_bench

Compilation log in wsrun.log

rm: cannot remove `wsrun.log': No such file or directory

Executing rm -rf __work dump.wlf dump.vcd diff.trace diff.ptrace archsim.trace archsim.ptrace verilogsim.trace verilogsim.ptrace

Executing vlib __work

** Warning: (vlib-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

No such file or directory. (errno = ENOENT)

Executing vlog +define+RANDSEED=3 -work __work clkrst.v shifter_hier_bench.v shifter_hier.v shifter.v

** Warning: (vlog-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

No such file or directory. (errno = ENOENT)

Model Technology ModelSim SE vlog 5.8b Compiler 2004.01 Jan 26 2004

-- Compiling module clkrst

-- Compiling module shifter_hier_bench

-- Compiling module shifter_hier

-- Compiling module shifter

Top level modules:

shifter_hier_bench

-------------------------------------------------

Step: 2

Running Verilog simulation...details in wsrun.log

Reading /afs/cs.wisc.edu/s/mentor-2004/common/modeltech-5.8b/tcl/vsim/pref.tcl

# ** Warning: (vish-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

# No such file or directory. (errno = ENOENT)

# 5.8b

# vsim -lib __work -c shifter_hier_bench

# // ModelSim SE 5.8b Jan 01 2004 Linux 2.6.32-573.7.1.el6.x86_64

# //

# // Copyright Model Technology, a Mentor Graphics Corporation company, 2004

# // All Rights Reserved.

# // UNPUBLISHED, LICENSED SOFTWARE.

# // CONFIDENTIAL AND PROPRIETARY INFORMATION WHICH IS THE

# // PROPERTY OF MENTOR GRAPHICS CORPORATION OR ITS LICENSORS.

# //

# ** Warning: (vsim-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

# No such file or directory. (errno = ENOENT)

# Loading __work.shifter_hier_bench

# Loading __work.shifter_hier

# Loading __work.clkrst

# Loading __work.shifter

VSIM 1> run -all

# TEST PASSED

# ** Note: $finish : shifter_hier_bench.v(27)

# Time: 5 us Iteration: 0 Instance: /shifter_hier_bench

-------------------------------------------------

Step: 3

Verilog simulation successful

Created a dump file dump.wlf.

To view waveforms, open with

vsim -view dataset=dump.wlf

Your design has passed the test if you do not see any error messages and receive the "TEST PASSED" message at the end of simulation. If your verilog had any syntax errors they would appear in step 1 and would prevent simulation.

Dealing with Errors

If your design wasn't fully functional on your first pass of running the testbench your message log will look slightly different:

-------------------------------------------------

Step: 1

Compiling the following verilog files: clkrst.v shifter_hier_bench.v shifter_hier.v shifter.v

Top module: shifter_hier_bench

Compilation log in wsrun.log

rm: cannot remove `wsrun.log': No such file or directory

Executing rm -rf __work dump.wlf dump.vcd diff.trace diff.ptrace archsim.trace archsim.ptrace verilogsim.trace verilogsim.ptrace

Executing vlib __work

** Warning: (vlib-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

No such file or directory. (errno = ENOENT)

Executing vlog +define+RANDSEED=3 -work __work clkrst.v shifter_hier_bench.v shifter_hier.v shifter.v

** Warning: (vlog-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

No such file or directory. (errno = ENOENT)

Model Technology ModelSim SE vlog 5.8b Compiler 2004.01 Jan 26 2004

-- Compiling module clkrst

-- Compiling module shifter_hier_bench

-- Compiling module shifter_hier

-- Compiling module shifter

Top level modules:

shifter_hier_bench

-------------------------------------------------

Step: 2

Running Verilog simulation...details in wsrun.log

Reading /afs/cs.wisc.edu/s/mentor-2004/common/modeltech-5.8b/tcl/vsim/pref.tcl

# ** Warning: (vish-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

# No such file or directory. (errno = ENOENT)

# 5.8b

# vsim -lib __work -c shifter_hier_bench

# // ModelSim SE 5.8b Jan 01 2004 Linux 2.6.32-573.7.1.el6.x86_64

# //

# // Copyright Model Technology, a Mentor Graphics Corporation company, 2004

# // All Rights Reserved.

# // UNPUBLISHED, LICENSED SOFTWARE.

# // CONFIDENTIAL AND PROPRIETARY INFORMATION WHICH IS THE

# // PROPERTY OF MENTOR GRAPHICS CORPORATION OR ITS LICENSORS.

# //

# ** Warning: (vsim-18) Environment variable MGC_LOCATION_MAP does not point to a valid path: "/u/j/o/johnston/mentor/.location".

# No such file or directory. (errno = ENOENT)

# Loading __work.shifter_hier_bench

# Loading __work.shifter_hier

# Loading __work.clkrst

# Loading __work.shifter

VSIM 1> run -all

# ERRORCHECK :: Shifter :: Shift Left : Count : 13, In = 5663 ; Expected : 6000, Got 6acc

# ERRORCHECK :: Shifter :: Shift Left : Count : 2, In = 8465 ; Expected : 1194, Got 1196

# ERRORCHECK :: Shifter :: Shift Left : Count : 6, In = cd0d ; Expected : 4340, Got 4373

# ERRORCHECK :: Shifter :: Shift Left : Count : 12, In = 57ed ; Expected : d000, Got d57e

# ERRORCHECK :: Shifter :: Rotate Left : Count : 5, In = 7ae8 ; Expected : 5d0f, Got 5d00

# ERRORCHECK :: Shifter :: Shift Left : Count : 13, In = 28bd ; Expected : a000, Got a517

# ERRORCHECK :: Shifter :: Rotate Left : Count : 10, In = 6263 ; Expected : 8d89, Got 8c00

# ERRORCHECK :: Shifter :: Shift Left : Count : 10, In = 2120 ; Expected : 8000, Got 8084

# ERRORCHECK :: Shifter :: Shift Left : Count : 3, In = 3e96 ; Expected : f4b0, Got f4b1

# ERRORCHECK :: Shifter :: Shift Left : Count : 11, In = d653 ; Expected : 9800, Got 9eb2

# ERRORCHECK :: Shifter :: Shift Left : Count : 14, In = 4a02 ; Expected : 8000, Got 9280

# ERRORCHECK :: Shifter :: Rotate Left : Count : 9, In = 3789 ; Expected : 126f, Got 1200

# ERRORCHECK :: Shifter :: Rotate Left : Count : 2, In = 7f0c ; Expected : fc31, Got fc30

# ERRORCHECK :: Shifter :: Shift Left : Count : 13, In = 007e ; Expected : c000, Got c00f

# ERRORCHECK :: Shifter :: Shift Left : Count : 3, In = 8f1f ; Expected : 78f8, Got 78fc

# ERRORCHECK :: Shifter :: Shift Left : Count : 11, In = 8878 ; Expected : c000, Got c443

# ERRORCHECK :: Shifter :: Rotate Left : Count : 10, In = ae3f ; Expected : feb8, Got fc00

# ERRORCHECK :: Shifter :: Rotate Left : Count : 14, In = 3886 ; Expected : 8e21, Got 8000

# ERRORCHECK :: Shifter :: Rotate Left : Count : 4, In = 1979 ; Expected : 9791, Got 9790

# ERRORCHECK :: Shifter :: Shift Left : Count : 10, In = addc ; Expected : 7000, Got 72b7

# ERRORCHECK :: Shifter :: Rotate Left : Count : 9, In = 8a38 ; Expected : 7114, Got 7000

# ERRORCHECK :: Shifter :: Rotate Left : Count : 3, In = bf94 ; Expected : fca5, Got fca0

# ERRORCHECK :: Shifter :: Shift Left : Count : 11, In = ca59 ; Expected : c800, Got ce52

# TEST FAILED

# ** Note: $finish : shifter_hier_bench.v(27)

# Time: 5 us Iteration: 0 Instance: /shifter_hier_bench

-------------------------------------------------

Step: 3

Verilog simulation successful

Created a dump file dump.wlf.

To view waveforms, open with

vsim -view dataset=dump.wlf

Notice the ERRORCHECK messages showing when a discrepancy was found between your design and a correctly functioning unit and that a "TEST FAILED" message is displayed at the end of simulation.

From here you could either stare at your verilog in confusion, stare at the error message values somewhat unhelpfully, or, much more useful, open a modelsim window that allows you to see the waveforms of all of the signals within your design. There are two ways of opening the wave window. The simulation you already ran will have output a dump.wlf file that can be opened by vsim with the command:

vsim -view dataset=dump.wlf

Or by adding the '-wave' option to the wsrun.pl command you used to run the simulation, e.g.:

wsrun.pl -wave shifter_hier_bench *.v

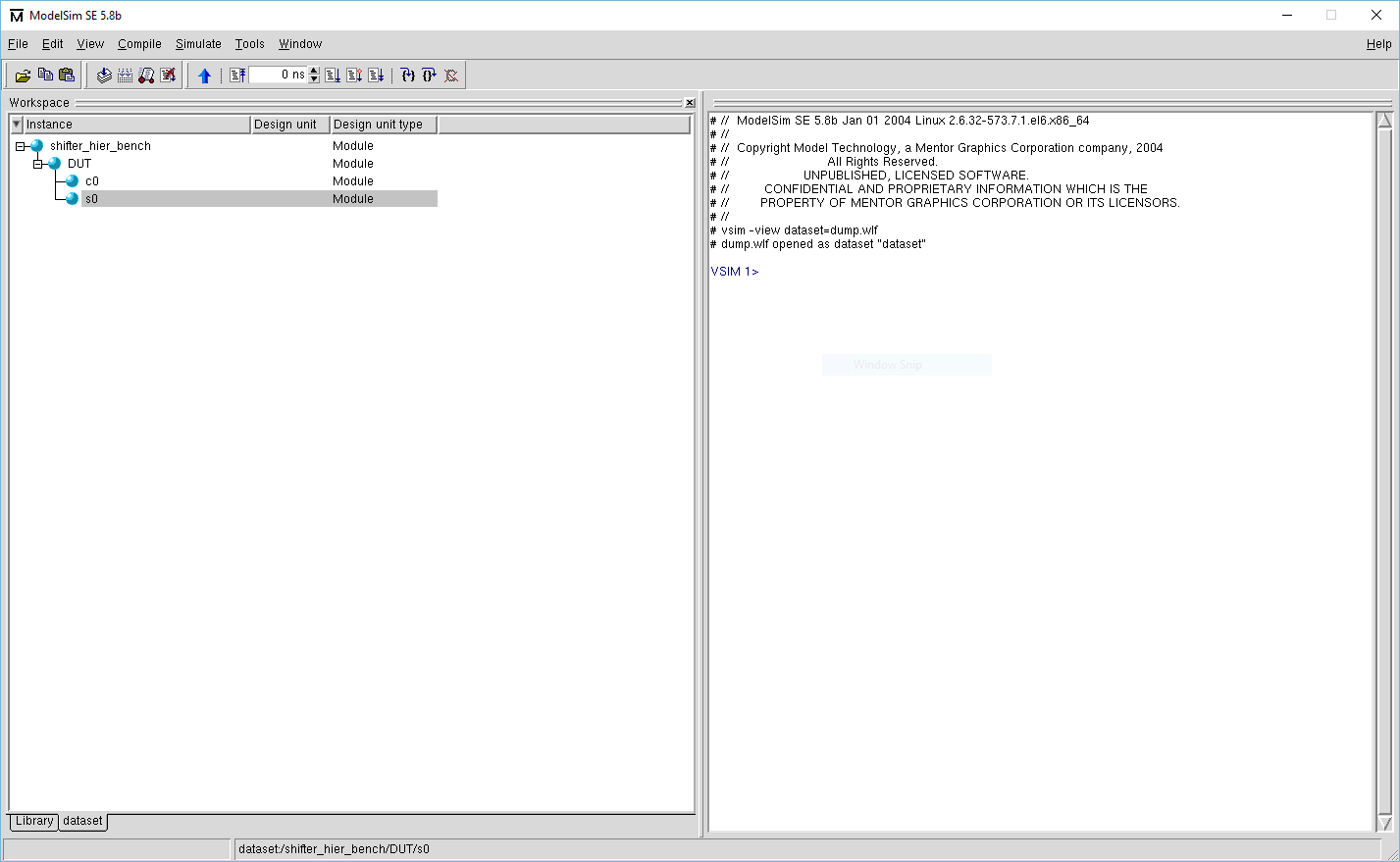

Running either command will bring up a window that looks like the following:

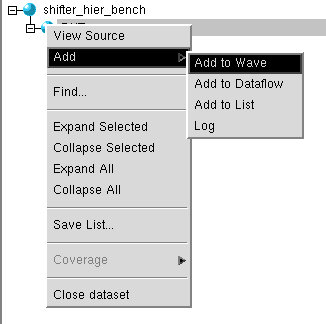

You can see your hierarchy of modules as instantiated from the testbench down. The signals for any given modules you want to look at can be added by right-clicking the module and choosing 'add to wave' as such:

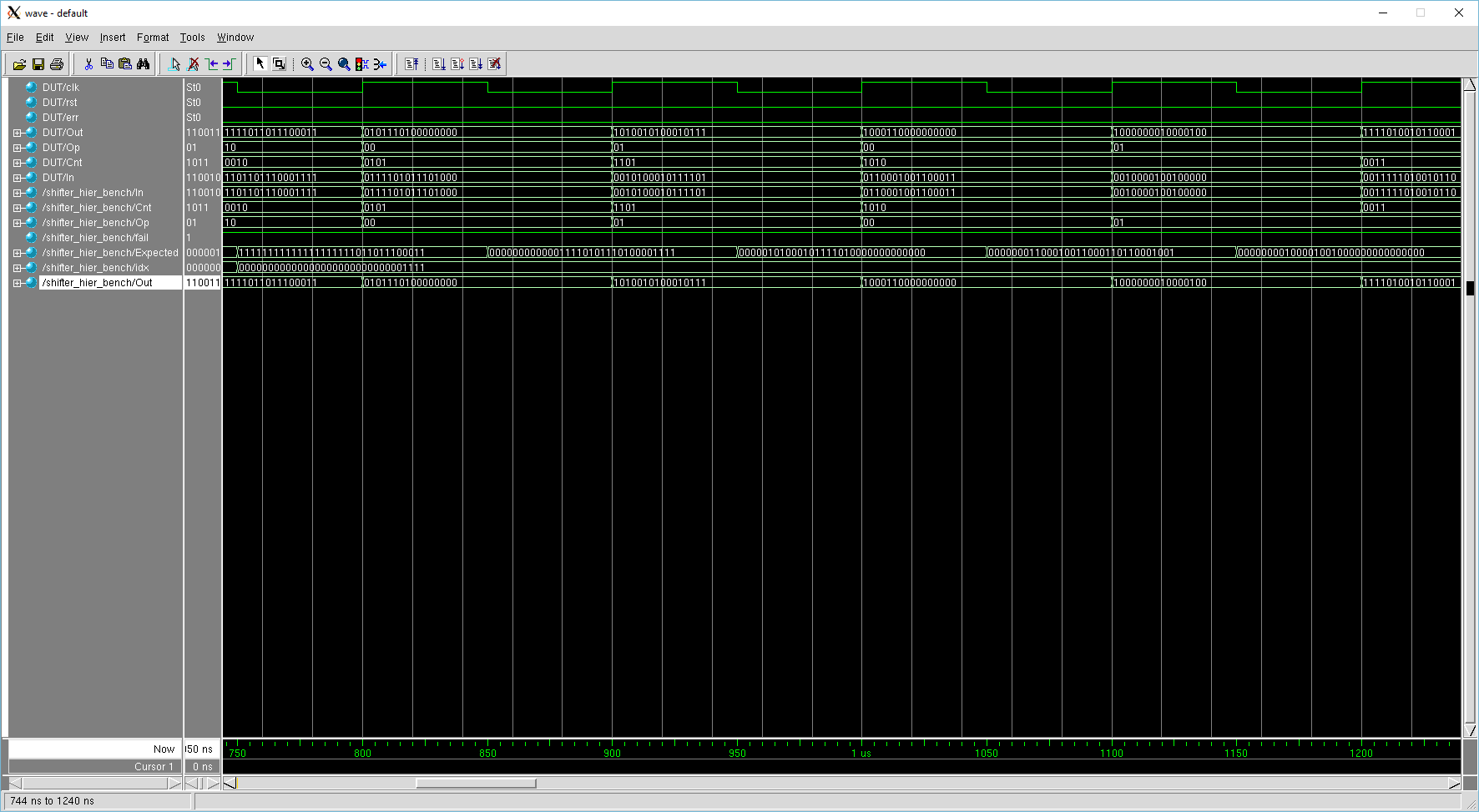

This will bring up the following window showing the signals within that module and their values throughout the entire simulation.

From here, the more subtle problems and module interactions that you might have and may not be apparent from the testbench error messages should be more manageable. In this particular case it can be seen that the shift left and rotate left operations have been swapped so I would likely want to look at the logic that uses the op-code to select which function is performed.